## Configuration Devices for SRAM-Based LUT Devices

CF52005-3.0 Datasheet

This datasheet describes configuration devices for SRAM-based look-up table (LUT) devices.

## **Supported Devices**

Table 1 lists the supported Altera® configuration devices.

**Table 1. Altera Configuration Devices**

| Device   | Memory Size (Bits) | ISP Support | Cascaded<br>Support | Reprogrammable | Recommended<br>Operating Voltage (V) |

|----------|--------------------|-------------|---------------------|----------------|--------------------------------------|

| EPC1     | 1,046,496          | No          | Yes                 | No             | 5.0 or 3.3                           |

| EPC2     | 1,695,680          | Yes         | Yes                 | Yes            | 5.0 or 3.3                           |

| EPC1064  | 65,536             | No          | No                  | No             | 5.0                                  |

| EPC1064V | 65,536             | No          | No                  | No             | 3.3                                  |

| EPC1213  | 212,942            | No          | Yes                 | No             | 5.0                                  |

| EPC1441  | 440,800            | No          | No                  | No             | 5.0 or 3.3                           |

### **Features**

Configuration devices for SRAM-based LUT devices offer the following features:

- Configures Altera ACEX® 1K, APEX™ 20K (including APEX 20K, APEX 20KC, and APEX 20KE), APEX II, Arria® GX, Cyclone®, Cyclone II, FLEX® 10K (including FLEX 10KE and FLEX 10KA) Mercury™, Stratix®, Stratix GX, Stratix II, and Stratix II GX devices

- Easy-to-use four-pin interface

- Low current during configuration and near-zero standby mode current

- Programming support with the Altera Programming Unit (APU) and programming hardware from Data I/O, BP Microsystems, and other third-party programmers

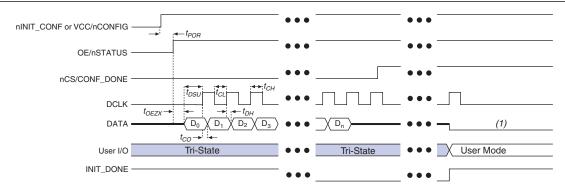

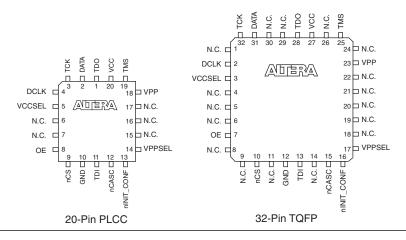

- Available in compact plastic packages

- 8-pin plastic dual in-line (PDIP) package

- 20-pin plastic J-lead chip carrier (PLCC) package

- 32-pin plastic thin quad flat pack (TQFP) package

- EPC2 device has reprogrammable flash configuration memory

© 2012 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Page 2 Functional Description

■ 5.0-V and 3.3-V in-system programmability (ISP) through the built-in IEEE Std. 1149.1 JTAG interface

- Built-in JTAG boundary-scan test (BST) circuitry compliant with IEEE Std. 1149.1

- Supports programming through Serial Vector Format File (.svf), Jam™ Standard Test and Programming Language (STAPL) Format File (.jam), JAM Byte Code File (.jbc), and the Quartus® II and MAX+PLUS® II softwares using the USB-Blaster™, MasterBlaster™, ByteBlaster™ II, EthernetBlaster, or ByteBlasterMV™ download cable

- Supports programming through Programmer Object File (.pof) for EPC1 and EPC1441 devices

- nINIT\_CONF pin allows INIT\_CONF JTAG instruction to begin FPGA configuration

- For more information about enhanced configuration (EPC) devices, refer to the *Enhanced Configuration (EPC) Devices Datasheet*.

- For more information about serial configuration (EPCS) devices, refer to the Serial Configuration (EPCS) Devices Datasheet.

## **Functional Description**

With SRAM-based devices, configuration data must be reloaded each time the device powers up, the system initializes, or when new configuration data is needed. Altera configuration devices store configuration data for SRAM-based ACEX 1K, APEX 20K, APEX II, Arria GX, Cyclone, Cyclone II, FLEX 10K, FLEX 6000, Mercury, Stratix, Stratix GX, Stratix II, and Stratix II GX devices.

Table 2 lists the supported configuration devices required to configure the ACEX 1K, APEX 20K, APEX 20KC, APEX 20KE, APEX II, Cyclone, Cyclone II, FLEX 10K, FLEX 10KA, FLEX 10KE, FLEX 6000/A, FLEX 8000A, Mercury, Stratix, Stratix GX, or Stratix II device.

| Table 2. | Supported | Configuration Devices | (Part 1 of 4) |

|----------|-----------|-----------------------|---------------|

|----------|-----------|-----------------------|---------------|

| Device Family | Device     | Data Size (Bits) | EPC1064 or<br>EPC1064V | EPC1213 | EPC1441 | EPC1 | EPC2 |

|---------------|------------|------------------|------------------------|---------|---------|------|------|

|               | EP1K10     | 159,160          | _                      | _       | 1       | 1    | 1    |

| ACEX 1K       | EP1K30     | 473,720          | _                      | _       | _       | 1    | 1    |

| AULX IX       | EP1K50     | 784,184          | _                      | _       | _       | 1    | 1    |

|               | EP1K100    | 1,335,720        | _                      | _       | _       | _    | 1    |

|               | EP20K100   | 993,360          | _                      | _       | _       | 1    | 1    |

| APEX 20K      | EP20K200   | 1,950,800        | _                      | _       | _       | _    | 2    |

|               | EP20K400   | 3,880,720        | _                      | _       | _       |      | 3    |

|               | EP20K200C  | 1,968,016        | _                      | _       | _       | _    | 2    |

| APEX 20KC     | EP20K400C  | 3,909,776        | _                      | _       | _       | _    | 3    |

|               | EP20K600C  | 5,673,936        | _                      | _       | _       | _    | 4    |

|               | EP20K1000C | 8,960,016        | _                      |         |         |      | 6    |

Functional Description Page 3

Table 2. Supported Configuration Devices (Part 2 of 4)

| Device Family | Device     | Data Size (Bits) | EPC1064 or<br>EPC1064V | EPC1213  | EPC1441 | EPC1  | EPC2  |

|---------------|------------|------------------|------------------------|----------|---------|-------|-------|

|               | EP20K30E   | 354,832          | _                      | _        | 1       | 1     | 1     |

|               | EP20K60E   | 648,016          | _                      | _        | _       | 1     | 1     |

|               | EP20K100E  | 1,008,016        | _                      | _        | _       | 1     | 1     |

|               | EP20K160E  | 1,524,016        | _                      | _        | _       | _     | 1     |

| ADEX OOKE     | EP20K200E  | 1,968,016        | _                      | _        | _       | _     | 2     |

| APEX 20KE     | EP20K300E  | 2,741,616        | _                      | _        | _       | _     | 2     |

|               | EP20K400E  | 3,909,776        | _                      | _        | _       | _     | 3     |

|               | EP20K600E  | 5,673,936        | _                      | _        | _       | _     | 4     |

|               | EP20K1000E | 8,960,016        | _                      | _        | _       | _     | 6     |

|               | EP20K1500E | 12,042,256       | _                      | _        | _       | _     | 8     |

|               | EP2A15     | 1,168,688        | _                      | _        | _       | _     | 3     |

| APEX II       | EP2A25     | 1,646,544        | _                      | _        | _       | _     | 4     |

| APEX II       | EP2A40     | 2,543,016        | _                      | _        | _       | _     | 6     |

|               | EP2A70     | 4,483,064        | _                      | _        | _       | _     | 11    |

|               | EP1C3      | 627,376          | _                      | _        | _       | 1     | 1     |

|               | EP1C4      | 925,000          | _                      | _        | _       | 1     | 1     |

| Cyclone       | EP1C6      | 1,167,216        | _                      | _        | _       | 1 (2) | 1     |

|               | EP1C12     | 2,326,528        | _                      | _        | _       | _     | 1 (2) |

|               | EP1C20     | 3,559,608        | _                      | _        | _       | _     | 2 (2) |

|               | EP2C5      | 1,265,792        | _                      | _        | _       | _     | 1     |

|               | EP2C8      | 1,983,536        | _                      | _        | _       | _     | 2     |

| Ovelene II    | EP2C20     | 3,892,496        | _                      | _        | _       | _     | 3     |

| Cyclone II    | EP2C35     | 6,848,608        | _                      | _        | _       | _     | 5     |

|               | EP2C50     | 9,951,104        | _                      | _        | _       | _     | 6     |

|               | EP2C70     | 14,319,216       | _                      | _        | _       | _     | 9     |

|               | EPF10K10   | 118,000          | _                      | _        | 1       | 1     | 1     |

|               | EPF10K20   | 231,000          | _                      | _        | 1       | 1     | 1     |

|               | EPF10K30   | 376,000          | _                      | _        | 1       | 1     | 1     |

| FLEX 10K      | EPF10K40   | 498,000          | _                      | _        | _       | 1     | 1     |

|               | EPF10K50   | 621,000          | _                      | _        | _       | 1     | 1     |

|               | EPF10K70   | 892,000          | _                      | _        | _       | 1     | 1     |

|               | EPF10K100  | 1,200,000        | _                      | _        | _       | _     | 1     |

|               | EPF10K10A  | 120,000          | _                      | _        | 1       | 1     | 1     |

|               | EPF10K30A  | 406,000          | _                      | _        | 1       | 1     | 1     |

| ELEV 101/A    | EPF10K50V  | 621,000          | _                      | _        | _       | 1     | 1     |

| FLEX 10KA     | EPF10K100A | 1,200,000        | _                      | <u> </u> | _       | _     | 1     |

|               | EPF10K130V | 1,600,000        | _                      | _        | _       | _     | 1     |

|               | EPF10K250A | 3,300,000        | _                      | _        | _       | _     | 2     |

Page 4 Functional Description

Table 2. Supported Configuration Devices (Part 3 of 4)

| Device Family | Device                         | Data Size (Bits) | EPC1064 or<br>EPC1064V | EPC1213 | EPC1441 | EPC1 | EPC2  |

|---------------|--------------------------------|------------------|------------------------|---------|---------|------|-------|

|               | EPF10K30E                      | 473,720          | _                      | _       | _       | 1    | 1     |

|               | EPF10K50E                      | 784,184          | _                      | _       | _       | 1    | 1     |

|               | EPF10K50S                      | 784,184          | _                      | _       | _       | 1    | 1     |

| FLEX 10KE     | EPF10K100B                     | 1,200,000        | _                      | _       | _       | _    | 1     |

| FLEX TUKE     | EPF10K100E                     | 1,335,720        | _                      | _       | _       | _    | 1     |

|               | EPF10K130E                     | 1,838,360        | _                      | _       | _       | _    | 2     |

|               | EPF10K200E                     | 2,756,296        | _                      | _       | _       | _    | 2     |

|               | EPF10K200S                     | 2,756,296        | _                      | _       | _       | _    | 2     |

|               | EPF6010A                       | 260,000          | _                      | _       | 1       | 1    | _     |

| FLEX 6000/A   | EPF6016(5.0 V)/<br>EPF6016A    | 260,000          | _                      | _       | 1       | 1    | _     |

|               | EPF6024A                       | 398,000          | _                      | _       | 1       | 1    | _     |

|               | EPF8282A /<br>EPF8282AV(3.3 V) | 40,000           | 1                      | 1       | 1       | 1    | _     |

|               | EPF8452A                       | 64,000           | 1                      | 1       | 1       | 1    | _     |

| FLEX 8000A    | EPF8636A                       | 96,000           | _                      | 1       | 1       | 1    | _     |

|               | EPF8820A                       | 128,000          | _                      | 1       | 1       | 1    | _     |

|               | EPF81188A                      | 192,000          | _                      | 1       | 1       | 1    | _     |

|               | EPF81500A                      | 250,000          | _                      | _       | 1       | 1    | _     |

| Morouni       | EP1M120                        | 1,303,120        | _                      | _       | _       | _    | 1     |

| Mercury       | EP1M350                        | 4,394,032        | _                      | _       | _       | _    | 3     |

|               | EP1S10                         | 3,534,640        | _                      | _       | _       | _    | 3 (3) |

|               | EP1S20                         | 5,904,832        | _                      | _       | _       | _    | 4     |

|               | EP1S25                         | 7,894,144        | _                      | _       | _       | _    | 5     |

| Stratix       | EP1S30                         | 10,379,368       | _                      | _       | _       | _    | 7     |

|               | EP1S40                         | 12,389,632       | _                      | _       | _       | _    | 8     |

|               | EP1S60                         | 17,543,968       | _                      | _       | _       | _    | 11    |

|               | EP1S80                         | 23,834,032       | _                      | _       | _       | _    | 15    |

|               | EP1SGX10                       | 3,534,640        | _                      | _       | _       | _    | 3     |

| Stratix GX    | EP1SGX25                       | 7,894,144        | _                      | _       | _       | _    | 5     |

|               | EP1SGX40                       | 12,389,632       | _                      | _       | _       | _    | 8     |

Functional Description Page 5

Table 2. Supported Configuration Devices (Part 4 of 4)

| Device Family | Device  | Data Size (Bits) | EPC1064 or<br>EPC1064V | EPC1213 | EPC1441 | EPC1 | EPC2 |

|---------------|---------|------------------|------------------------|---------|---------|------|------|

|               | EP2S15  | 5,000,000        | _                      | _       | _       | _    | 3    |

|               | EP2S30  | 10,100,000       | _                      | _       | _       | _    | 7    |

| Stratix II    | EP2S60  | 17,100,000       | _                      | _       | _       | _    | 11   |

| Stratix II    | EP2S90  | 27,500,000       | _                      | _       | _       | _    | 17   |

|               | EP2S130 | 39,600,000       | _                      | _       | _       | _    | 24   |

|               | EP2S180 | 52,400,000       | _                      | _       | _       | _    | 31   |

#### Notes to Table 2:

- (1) Raw Binary File (.rbf) were used to determine these sizes.

- (2) This number is calculated with the Cyclone series compression feature enabled.

- (3) EP1S10 ES devices requires four EPC2 devices.

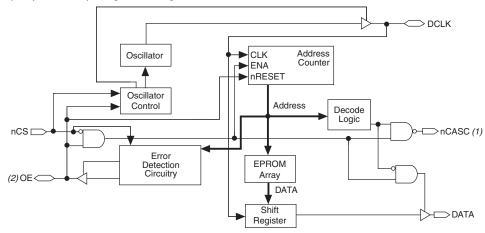

Figure 1 shows the configuration device block diagram.

Figure 1. Configuration Device Block Diagram

FPGA (except FLEX 8000) Configuration Using an EPC2, EPC1, or EPC1441

#### FLEX 8000 Device Configuration Using an EPC1, EPC1441, EPC1213, EPC1064, or EPC1064V

#### Notes to Figure 1:

- (1) The EPC1441 devices do not support data cascading. The EPC1, EPC2, and EPC1213 devices support data cascading.

- (2) The OE pin is a bidirectional open-drain pin.

Page 6 Device Configuration

## **Device Configuration**

The EPC1, EPC2, and EPC1441 devices store configuration data in its erasable programmable read-only memory (EPROM) array and serially clock data out using an internal oscillator. The OE, nCS, and DCLK pins supply the control signals for the address counter and the DATA output tri-state buffer. The configuration device sends a serial bitstream of configuration data to its DATA pin, which is routed to the DATAO input of the FPGA.

The control signals for configuration devices, OE, nCS, and DCLK, interface directly with the FPGA control signals, nSTATUS, CONF\_DONE, and DCLK. All Altera FPGAs can be configured by a configuration device without requiring an external intelligent controller.

An EPC2 device cannot configure FLEX 8000 or FLEX 6000 devices. For configuration devices that support FLEX 8000 or FLEX 6000 devices, refer to Table 2.

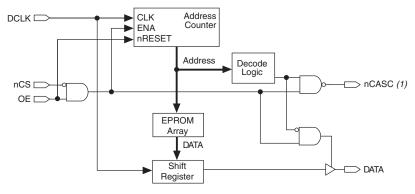

Figure 2 shows the basic configuration interface connections between the configuration device and the Altera FPGA.

Figure 2. Altera FPGA Configured Using an EPC1, EPC2, or EPC1441 Configuration Device (1)

#### Notes to Figure 2:

- (1) For more information about configuration interface connections, refer to the configuration chapter in the appropriate device handbook.

- (2) The ninit\_conf pin which is available on EPC2 devices has an internal pull-up resistor that is always active. This means an external pull-up resistor is not required on the ninit\_conf/nconf/gline. The ninit\_conf pin does not need to be connected if its functionality is not used. If the ninit\_conf pin is not used or unavailable, nconfig must be pulled to V<sub>CC</sub> either directly or through a resistor.

- (3) EPC2 devices have internal programmable pull-up resistors on OE and ncs pins. If internal pull-up resistors are used, do not use external pull-up resistors on these pins. The internal pull-up resistors are set by default in the Quartus II software. To turn off the internal pull-up resistors, check the **Disable ncs and OE pull-ups on configuration device** option when you generate programming files.

The EPC2 device allows you to begin configuration of the FPGA using an additional pin, nINIT\_CONF. The nINIT\_CONF pin of the EPC2 device can be connected to the nCONFIG pin of the FPGA, which allows the INIT\_CONF JTAG instruction to begin FPGA configuration. The INIT\_CONF JTAG instruction causes the EPC2 device to drive the nINIT\_CONF pin low, which in turn pulls the nCONFIG pin low. Pulling the nCONFIG pin low on the FPGA will reset the device. When the JTAG state machine exits this state, the nINIT\_CONF pin is released and pulled high by an internal 1-k $\Omega$  resistor, which in turn pulls the nCONFIG pin high to begin configuration. If you do not use the nINIT\_CONF pin, disconnect the nINIT\_CONF pin, and pull the nCONFIG pin of the FPGA to VCC either directly or through a resistor.

Device Configuration Page 7

The EPC2 device's OE and nCS pins have internal programmable pull-up resistors. If you use internal pull-up resistors, do not use external pull-up resistors on these pins. The internal pull-up resistors are set by default in the Quartus II software. To turn off the internal pull-up resistors, check the **Disable nCS and OE pull-ups on configuration device** option when you generate programming files.

The configuration device's OE and nCS pins control the tri-state buffer on its DATA output pin and enable the address counter and oscillator. When the OE pin is driven low, the configuration device resets the address counter and tri-states its DATA pin. The nCS pin controls the DATA output of the configuration device. If the nCS pin is held high after the OE reset pulse, the counter is disabled and the DATA output pin is tri-stated. If the nCS pin is driven low after the OE reset pulse, the counter and DATA output pin are enabled. When OE is driven low again, the address counter is reset and the DATA output pin is tri-stated, regardless of the state of the nCS pin.

If the FPGA's configuration data exceeds the capacity of a single EPC1 or EPC2 configuration device, you can cascade multiple EPC1 or EPC2 devices together. If multiple EPC1 or EPC2 devices are required, the nCASC and nCS pins provide handshaking between the configuration devices.

EPC1441 and EPC1064/EPC1064V devices cannot be cascaded.

When configuring ACEX 1K, APEX 20K, APEX II, Arria GX, Cyclone, Cyclone II, FLEX 10K, Mercury, Stratix, Stratix GX, Stratix II, and Stratix II GX devices with cascaded EPC1 or EPC2 devices, the position of the EPC1 or EPC2 device in the chain determines its mode of operation. The first configuration device in the chain is the master, while subsequent configuration devices are slaves. The nINIT\_CONF pin of the EPC2 master device can be connected to the nCONFIG pin of the FPGAs, which allows the INIT\_CONF JTAG instruction to begin FPGA configuration. The nCS pin of the master configuration device is connected to the configuration of the FPGAs, while its nCASC pin is connected to the nCS pin of the next slave configuration device in the chain. Additional EPC1 or EPC2 devices can be chained together by connecting the nCASC pin to the nCS pin of the next EPC1 or EPC2 slave device in the chain. The last device's nCS input comes from the previous device, while its nCASC pin is left floating. All other configuration pins, DCLK, DATA, and OE, are connected to every device in the chain.

For more information about configuration interface connections, including pull-up resistor values, supply voltages, and MSEL pin setting, refer to the configuration chapter in the appropriate device handbook.

Page 8 Device Configuration

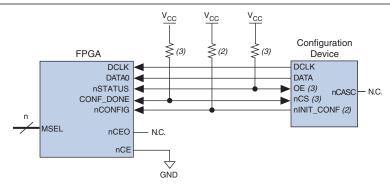

Figure 3 shows the basic configuration interface connections between a configuration device chain and the Altera FPGA.

Figure 3. Altera FPGA Configured Using Two EPC1 or EPC2 Configuration Devices (1)

#### Notes to Figure 3:

- (1) For more information about configuration interface connections, refer to the configuration chapter in the appropriate device handbook.

- (2) The ninit\_conf pin which is available on EPC2 devices has an internal pull-up resistor that is always active. This means an external pull-up resistor is not required on the ninit\_conf/nconfig line. The ninit\_conf pin does not need to be connected if its functionality is not used. If the ninit\_conf pin is not used or unavailable, nconfig must be pulled to V<sub>CC</sub> either directly or through a resistor.

- (3) EPC2 devices have internal programmable pull-up resistors on OE and nCS pins. If internal pull-up resistors are used, do not use external pull-up resistors on these pins. The internal pull-up resistors are set by default in the Quartus II software. To turn off the internal pull-up resistors, check the **Disable nCS and OE pull-ups on configuration device** option when you generate programming files.

When the first device in a configuration device chain is powered-up or reset, its nCS pin is driven low because it is connected to the CONF\_DONE pin of the FPGA. Because both OE and nCS pins are low, the first device in the chain recognizes it as the master device and controls configuration. Since the slave devices' nCS pin is fed by the previous devices' nCASC pin, its nCS pin is high after power-up and reset. In the slave configuration devices, the DATA output is tri-stated and DCLK is an input. During configuration, the master device supplies the clock through DCLK to the FPGA and to any slave configuration devices. The EPC1 or EPC2 master device also provides the first stream of data to the FPGA during multi-device configuration. After the EPC1 or EPC2 master device finishes sending configuration data, it tri-states its DATA pin to avoid contention with other configuration devices. The EPC1 or EPC2 master device also drives its nCASC pin low, which pulls the nCS pin of the next device low. This action signals the EPC1 or EPC2 slave device to start sending configuration data to the FPGAs.

The EPC1 or EPC2 master device clocks all slave configuration devices until configuration is complete. When all configuration data is transferred and the nCS pin on the EPC1 or EPC2 master device is driven high by the FPGA's CONF\_DONE pin, the EPC1 or EPC2 master device then goes into zero-power (idle) state. The EPC2 master device drives DATA high and DCLK low, while the EPC1 and EPC1441 device tri-state DATA and drive DCLK low.

If the nCS pin on the EPC1 or EPC2 master device is driven high before all configuration data is transferred, the EPC1 or EPC2 master device drives its OE signal low, which in turn drives the FPGA's nSTATUS pin low, indicating a configuration error. Additionally, if the configuration device generates its data and detects that the CONF\_DONE pin has not gone high, it recognizes that the FPGA has not configured successfully. EPC1 and EPC2 devices wait for 16 DCLK cycles after the last

Power and Operation Page 9

configuration bit was sent for the CONF\_DONE pin to reach a high state. In this case, the configuration device pulls its OE pin low, which in turn drives the target device's <code>nSTATUS</code> pin low. Configuration automatically restarts if the **Auto-restart** configuration on error option is turned on in the Quartus II software from the General tab of the Device & Pin Options dialog box or the MAX+PLUS II software's Global Project Device Options dialog box (Assign menu).

For more information about FPGA configuration and configuration interface connections between configuration devices and Altera FPGAs, refer to the configuration chapter in the appropriate device handbook.

## **Power and Operation**

This section describes power-on reset (POR) delay, error detection, and 3.3-V and 5.0-V operation of Altera configuration devices.

### **Power-On Reset**

During initial power-up, a POR delay occurs to permit voltage levels to stabilize. When configuring an FPGA with one EPC1, EPC2, or EPC1441 device, the POR delay occurs inside the configuration device and the POR delay is a maximum of 200 ms. When configuring a FLEX 8000 device with one EPC1213, EPC1064, or EPC1064V device, the POR delay occurs inside the FLEX 8000 device and the POR delay is typically 100 ms, with a maximum of 200 ms.

During POR, the configuration device drives its OE pin low. This low signal delays configuration because the OE pin is connected to the target FPGA's nSTATUS pin. When the configuration device completes POR, it releases its open-drain OE pin, which is then pulled high by a pull-up resistor.

You should power up the FPGA before the configuration device exits POR to avoid the master configuration device from entering slave mode.

If the FPGA is not powered up before the configuration device exits POR, the  $CONF_DONE/nCS$  line is high because of the pull-up resistor. When the configuration device exits POR and releases OE, it sees nCS high, which signals the configuration device to enter slave mode. Therefore, configuration will not begin because the DATA output is tri-stated and DCLK is an input pin in slave mode.

## **Error Detection Circuitry**

The EPC1, EPC2, and EPC1441 configuration devices have built-in error detection circuitry for configuring ACEX 1K, APEX 20K, APEX II, Arria GX, Cyclone, Cyclone II, FLEX 10K, FLEX 6000, Mercury, Stratix, Stratix GX, Stratix II, or Stratix II GX devices.

Built-in error detection circuitry uses the nCS pin of the configuration device, which monitors the CONF\_DONE pin on the FPGA. If the nCS pin on the EPC1 or EPC2 master device is driven high before all configuration data is transferred, the EPC1 or EPC2 master device drives its OE signal low, which in turn drives the FPGA's nSTATUS pin low, indicating a configuration error. Additionally, if the configuration device generates its data and detects that the CONF\_DONE pin has not gone high, it recognizes

Page 10 Power and Operation

that the FPGA has not configured successfully. EPC1 and EPC2 devices wait for 16 DCLK cycles after the last configuration bit was sent for the CONF\_DONE pin to reach a high state. In this case, the configuration device pulls its OE pin low, which in turn drives the target device's nSTATUS pin low. Configuration automatically restarts if the Auto-restart configuration on error option is turned on in the Quartus II software from the General tab of the Device & Pin Options dialog box or the MAX+PLUS II software's Global Project Device Options dialog box (Assign menu).

In addition, if the FPGA detects a cyclic redundancy check (CRC) error in the received data, it will flag the error by driving the *n*STATUS signal low. This low signal on *n*STATUS drives the OE pin of the configuration device low, which resets the configuration device. CRC checking is performed when configuring all Altera FPGAs.

### 3.3-V or 5.0-V Operation

Power the EPC1, EPC2, and EPC 1441 configuration device at 3.3 V or 5.0 V. For each configuration device, an option must be set for the 3.3-V or 5.0-V operation.

For EPC1 and EPC1441 configuration devices, 3.3-V or 5.0-V operation is controlled by a programming bit in the **.pof**. The **Low-Voltage mode** option in the Options tab of the Configuration Device Options dialog box in the Quartus II software or the **Use Low-Voltage Configuration EPROM** option in the **Global Project Device Options** dialog box (Assign menu) in the MAX+PLUS II software sets this parameter. For example, EPC1 devices are programmed automatically to operate in 3.3-V mode when configuring FLEX 10KA devices, which have a  $V_{CC}$  voltage of 3.3 V. In this example, the EPC1 device's VCC pin is connected to a 3.3-V power supply.

For EPC2 devices, this option is set externally by the VCCSEL pin. In addition, the EPC2 device has an externally controlled option, set by the VPPSEL pin, to adjust the programming voltage to 5.0 V or 3.3 V. The functions of the VCCSEL and VPPSEL pins are described below. These pins are only available in the EPC2 devices.

- VCCSEL pin—For EPC2 configuration devices, 5.0-V or 3.3-V operation is controlled by the VCCSEL option pin. The device functions in 5.0-V mode when VCCSEL is connected to GND and 3.3-V mode when VCCSEL is connected to  $V_{CC}$ .

- VPPSEL pin—The  $V_{PP}$  programming power pin of the EPC2 device is normally tied to  $V_{CC}$ . For EPC2 devices operating at 3.3 V, it is possible to improve ISP time by setting  $V_{PP}$  to 5.0 V. For all other configuration devices,  $V_{PP}$  must be tied to  $V_{CC}$ . The VPPSEL pin of the EPC2 device must be set in accordance with the VPP pin of the EPC2 device. If the VPP pin is supplied by a 5.0-V power supply, VPPSEL must be connected to GND and if the VPP pin is supplied by a 3.3-V power supply, VPPSEL must be connected to  $V_{CC}$ .

Power and Operation Page 11

Table 3 lists the relationship between the  $V_{CC}$  and  $V_{PP}$  voltage levels and the required logic level for VCCSEL and VPPSEL pins. A high logic level means the pin should be connected to  $V_{CC}$ , while a low logic level means the pin should be connected to GND.

Table 3. VCCSEL and VPPSEL Pin Functions on the EPC2 Device

| VCC Voltage Level<br>(V) | VPP Voltage Level<br>(V) | VCCSEL Pin Logic<br>Level | VPPSEL Pin Logic<br>Level |

|--------------------------|--------------------------|---------------------------|---------------------------|

| 3.3                      | 3.3                      | High                      | High                      |

| 3.3                      | 5.0                      | High                      | Low                       |

| 5.0                      | 5.0                      | Low                       | Low                       |

At a 3.3-V operation, all EPC2 inputs are 5.0-V tolerant, except for DATA, DCLK, and nCASC pins. The DATA and DCLK pins are used only to interface between the EPC2 device and the FPGA it is configuring. Table 4 lists the voltage tolerences of all EPC2 device pins.

Table 4. EPC2 Device Input and Bidirectional Pin Voltage Tolerance

| Pin           | 5.0-V 0        | peration       | 3.3-V Operation |                |  |

|---------------|----------------|----------------|-----------------|----------------|--|

| riii          | 5.0-V Tolerant | 3.3-V Tolerant | 5.0-V Tolerant  | 3.3-V Tolerant |  |

| DATA          | ✓              | ✓              | _               | ✓              |  |

| DCLK          | ✓              | <b>✓</b>       | _               | <b>✓</b>       |  |

| <i>n</i> CASC | ✓              | <b>✓</b>       | _               | <b>✓</b>       |  |

| OE            | ✓              | ✓              | ✓               | ✓              |  |

| ncs           | ✓              | ✓              | ✓               | ✓              |  |

| VCCSEL        | ✓              | <b>✓</b>       | <b>✓</b>        | ✓              |  |

| VPPSEL        | ✓              | ✓              | ✓               | ✓              |  |

| ninit_conf    | ✓              | <b>✓</b>       | <b>✓</b>        | ✓              |  |

| TDI           | ✓              | <b>✓</b>       | <b>✓</b>        | ✓              |  |

| TMS           | ✓              | <b>✓</b>       | <b>✓</b>        | ✓              |  |

| TCK           | ✓              | ✓              | ✓               | ✓              |  |

If one EPC1, EPC2, or EPC1441 configuration device is powered at 3.3 V, the *n*STATUS and CONF\_DONE pull-up resistors must be connected to 3.3 V. If these configuration devices are powered at 5.0 V, the *n*STATUS and CONF\_DONE pull-up resistors can be connected to either 3.3 V or 5.0 V.

## **Programming and Configuration File Support**

The Quartus II and MAX+PLUS II softwares provide programming support for Altera configuration devices. During compilation, the Quartus II and MAX+PLUS II softwares automatically generates a .pof, which is used to program the configuration devices. In a multi-device configuration, the software combines the programming files for multiple ACEX 1K, APEX 20K, APEX II, Arria GX, Cyclone, Cyclone II, FLEX 10K, Mercury, Stratix, Stratix GX, Stratix II, and Stratix II GX devices into one or more configuration devices. The software allows you to select the appropriate configuration device to store the data for each FPGA.

All Altera configuration devices are programmable using Altera programming hardware in conjunction with the Quartus II or MAX+PLUS II software. In addition, many third-party programmers offer programming hardware that supports Altera configuration devices.

An EPC2 device can be programmed with a **.pof** generated for an EPC1 or EPC1441 device. An EPC1 device can be programmed with a **.pof** generated for an EPC1441 device.

EPC2 configuration devices can be programmed in-system through its industry-standard four-pin JTAG interface. ISP capability in the EPC2 devices provide ease in prototyping and FPGA functionality. When programming multiple EPC2 devices in a JTAG chain, the Quartus II and MAX+PLUS II softwares and other programming methods employ concurrent programming to simultaneously program multiple devices and reduce programming time. EPC2 devices can be programmed and erased up to 100 times.

After programming an EPC2 device in-system, FPGA configuration is initiated by the INIT\_CONF JTAG instruction of the EPC2 device. For more information, refer to Table 6.

- Altera Programming Hardware Data Sheet

- USB-Blaster Download Cable User Guide

- MasterBlaster Serial/USB Communications Cable User Guide

- ByteBlaster II Download Cable User Guide

- ByteBlasterMV Download Cable User Guide

- BitBlaster Serial Download Cable Data Sheet

You can also program the configuration devices using the Quartus II or MAX+PLUS II software with the APU or the appropriate configuration device programming adapter.

Table 5 lists the programming adapter to use with each configuration device.

**Table 5. Programming Adapters**

| Device  | Package       | Adapter  |

|---------|---------------|----------|

| EPC2    | 20-pin J-Lead | PLMJ1213 |

| LI UZ   | 32-pin TQFP   | PLMT1213 |

| EPC1    | 8-pin DIP     | PLMJ1213 |

| LFUI    | 20-pin J-Lead | PLMJ1213 |

|         | 8-pin DIP     | PLMJ1213 |

| EPC1441 | 20-pin J-Lead | PLMJ1213 |

|         | 32-pin TQFP   | PLMT1064 |

To program Altera configuration devices using the Quartus II software and the APU, follow these steps:

- 1. Choose the **Quartus II Programmer** (Tools menu).

- 2. Load the appropriate **.pof** by clicking **Add**. The **Device** column displays the device for the current programming file.

- 3. Insert a blank configuration device into the programming adapter's socket.

- 4. Turn on the **Program/Configure**. You can also turn on **Verify** to verify the contents of a programmed device against the programming data loaded from a programming file.

- 5. Click Start.

- 6. After successful programming, you can place the configuration device on the PCB to configure the FPGA device.

To program Altera configuration devices using the MAX+PLUS II software and the APU, follow these steps:

- 1. Open the MAX+PLUS II Programmer.

- 2. Load the appropriate .pof using the Select Programming File dialog box (File menu). By default, the Programmer loads the current project's .pof. The Device field displays the device for the current programming file.

- 3. Insert a blank configuration device into the programming adapter's socket.

- 4. Click Program.

- 5. After successful programming, you can place the configuration device on the PCB to configure the FPGA device.

If you are cascading EPC1 or EPC2 devices, you must generate multiple .pof. The first device .pof have the same name as the project, while the second device .pof have the same name as the first, but with a "\_1" extension (e.g., top\_1.pof).

# IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing

The EPC2 device provides JTAG BST circuitry that complies with the IEEE Std. 1149.1-1990 specification. You can perform JTAG BST before or after configuration, but not during configuration. Table 6 lists the JTAG instructions supported by the EPC2 device.

Table 6. EPC2 Device JTAG Instructions

| JTAG Instruction | OPCODE       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SAMPLE/PRELOAD   | 00 0101 0101 | Allows a snapshot of a signal at the device pins to be captured and examined during normal device operation and permits an initial data pattern output at the device pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| EXTEST           | 00 0000 0000 | Allows the external circuitry and board-level interconnections to be tested by forcing a test pattern at the output pins and capturing results at the input pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| BYPASS           | 11 1111 1111 | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through a selected device to adjacent devices during normal device operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| IDCODE           | 00 0101 1001 | Selects the device IDCODE register and places it between the TDI and TDO pins, allowing the device IDCODE to be serially shifted out of the TDO pin. The device IDCODE for the EPC2 configuration device is shown below:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                  |              | 0000 000100000000010 00001101110 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| USERCODE         | 00 0111 1001 | Selects the USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of the TDO pin. The 32-bit USERCODE is a programmable user-defined pattern.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| INIT_CONF        | 00 0110 0001 | Initiates the FPGA re-configuration process by pulsing the <code>ninit_CONF</code> pin low, which is connected to the FPGAs <code>nconfig</code> pins. After this instruction is updated, the <code>ninit_CONF</code> pin is pulsed low when the JTAG state machine enters the Run-Test/Idle state. The <code>ninit_CONF</code> pin is then released and <code>nconfig</code> is pulled high by the resistor after the JTAG state machine goes out of Run-Test/Idle state. The FPGA configuration starts after the <code>nconfig</code> pin goes high. As a result, the FPGA is configured with the new configuration data stored in the configuration device. You can add this function to your programming file ( <code>.pof</code> , <code>.jam</code> , <code>.jbc</code> ) in the Quartus II software by enabling the <code>Initiate</code> configuration after programming option in the Programmer options window (Options menu). This instruction is also used by the MAX+PLUS II software, <code>.jam</code> files, and <code>.jbc</code> files. |

| ISP Instructions | _            | These instructions are used when programming an EPC2 device using JTAG ports with a USB-Blaster, MasterBlaster, ByteBlaster II, EthernetBlaster, or ByteBlasterMV download cable, or using a .jam, .jbc, or .svf file using an embedded processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

For more information, refer to AN39: IEEE 1149.1 JTAG Boundary-Scan Testing in Altera Devices.

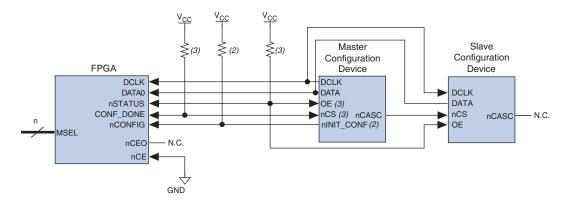

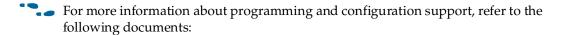

Figure 4 shows the timing requirements for the JTAG signals.

Figure 4. EPC2 Device JTAG Waveforms

Table 7 lists the timing parameters and values for configuration devices.

**Table 7. JTAG Timing Parameters and Values**

| Symbol            | Parameter                                      | Min | Max | Unit |

|-------------------|------------------------------------------------|-----|-----|------|

| t <sub>JCP</sub>  | TCK clock period                               | 100 | _   | ns   |

| t <sub>JCH</sub>  | TCK clock high time                            | 50  | _   | ns   |

| t <sub>JCL</sub>  | TCK clock low time                             | 50  | _   | ns   |

| t <sub>JPSU</sub> | JTAG port setup time                           | 20  | _   | ns   |

| t <sub>JPH</sub>  | JTAG port hold time                            | 45  | _   | ns   |

| t <sub>JPCO</sub> | JTAG port clock to output                      | _   | 25  | ns   |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output       | _   | 25  | ns   |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance       | _   | 25  | ns   |

| t <sub>JSSU</sub> | Capture register setup time                    | 20  | _   | ns   |

| t <sub>JSH</sub>  | Capture register hold time                     | 45  | _   | ns   |

| t <sub>JSCO</sub> | Update register clock to output                | _   | 25  | ns   |

| t <sub>JSZX</sub> | Update register high impedance to valid output | _   | 25  | ns   |

| t <sub>JSXZ</sub> | Update register valid output to high impedance | _   | 25  | ns   |

Page 16 Timing Information

## **Timing Information**

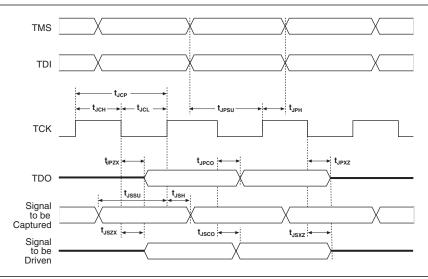

Figure 5 shows the timing waveform when using a configuration device.

Figure 5. Timing Waveform Using a Configuration Device

#### Note to Figure 5:

(1) The EPC2 device drives DCLK low and DATA high after configuration. The EPC1 and EPC1441 devices drive DCLK low and tri-state DATA after configuration.

Table 8 lists the timing parameters when using EPC2 devices at 3.3 V.

Table 8. Timing Parameters when Using EPC2 devices at 3.3 V

| Symbol             | Parameter                                                      | Min | Тур | Max  | Units |

|--------------------|----------------------------------------------------------------|-----|-----|------|-------|

| t <sub>POR</sub>   | POR delay (1)                                                  | _   | _   | 200  | ms    |

| t <sub>OEZX</sub>  | OE high to DATA output enabled                                 | _   |     | 80   | ns    |

| t <sub>CE</sub>    | OE high to first rising edge on DCLK                           |     |     | 300  | ns    |

| t <sub>DSU</sub>   | Data setup time before rising edge on DCLK                     | 30  | _   | _    | ns    |

| t <sub>DH</sub>    | Data hold time after rising edge on DCLK                       | 0   |     | _    | ns    |

| t <sub>co</sub>    | DCLK to DATA out                                               |     |     | 30   | ns    |

| t <sub>CDOE</sub>  | DCLK to DATA enable/disable                                    | _   | _   | 30   | ns    |

| f <sub>CLK</sub>   | DCLK frequency                                                 | 5   | 7.7 | 12.5 | MHz   |

| t <sub>MCH</sub>   | DCLK high time for the first device in the configuration chain | 40  | 65  | 100  | ns    |

| t <sub>MCL</sub>   | DCLK low time for the first device in the configuration chain  | 40  | 65  | 100  | ns    |

| t <sub>SCH</sub>   | DCLK high time for subsequent devices                          | 40  |     | _    | ns    |

| t <sub>SCL</sub>   | DCLK low time for subsequent devices                           | 40  |     | _    | ns    |

| t <sub>CASC</sub>  | DCLK rising edge to nCASC                                      | _   | _   | 25   | ns    |

| t <sub>CCA</sub>   | nCS to nCASC cascade delay                                     | _   |     | 15   | ns    |

| t <sub>OEW</sub>   | OE low pulse width (reset) to guarantee counter reset          | 100 | _   | _    | ns    |

| t <sub>OEC</sub>   | OE low (reset) to DCLK disable delay                           |     | _   | 30   | ns    |

| t <sub>NRCAS</sub> | OE low (reset) to nCASC delay                                  |     |     | 30   | ns    |

#### Note to Table 8:

(1) During initial power-up, a POR delay occurs to permit voltage levels to stabilize. Subsequent reconfigurations do not incur this delay.

Timing Information Page 17

Table 9 lists the timing parameters when using EPC1 and EPC1441 devices at 3.3 V.

Table 9. Timing Parameters when Using EPC1 and EPC1441 Devices at 3.3 V

| Symbol             | Parameter                                                      | Min | Тур | Max | Units |

|--------------------|----------------------------------------------------------------|-----|-----|-----|-------|

| t <sub>POR</sub>   | POR delay (1)                                                  | _   | _   | 200 | ms    |

| t <sub>OEZX</sub>  | OE high to DATA output enabled                                 | _   | _   | 80  | ns    |

| t <sub>CE</sub>    | OE high to first rising edge on DCLK                           | _   | _   | 300 | ns    |

| t <sub>DSU</sub>   | Data setup time before rising edge on DCLK                     | 30  | _   | _   | ns    |

| t <sub>DH</sub>    | Data hold time after rising edge on DCLK                       | 0   | _   | _   | ns    |

| t <sub>CO</sub>    | DCLK to DATA out                                               | _   | _   | 30  | ns    |

| t <sub>CDOE</sub>  | DCLK to DATA enable/disable                                    | _   | _   | 30  | ns    |

| f <sub>CLK</sub>   | DCLK frequency                                                 | 2   | 4   | 10  | MHz   |

| t <sub>MCH</sub>   | DCLK high time for the first device in the configuration chain | 50  | 125 | 250 | ns    |

| t <sub>MCL</sub>   | DCLK low time for the first device in the configuration chain  | 50  | 125 | 250 | ns    |

| t <sub>SCH</sub>   | DCLK high time for subsequent devices                          | 50  | _   | _   | ns    |

| t <sub>SCL</sub>   | DCLK low time for subsequent devices                           | 50  | _   | _   | ns    |

| t <sub>CASC</sub>  | DCLK rising edge to nCASC                                      | _   | _   | 25  | ns    |

| t <sub>CCA</sub>   | nCS to nCASC cascade delay                                     | _   | _   | 15  | ns    |

| t <sub>OEW</sub>   | OE low pulse width (reset) to guarantee counter reset          | 100 | _   | _   | ns    |

| t <sub>OEC</sub>   | OE low (reset) to DCLK disable delay                           | _   | _   | 30  | ns    |

| t <sub>NRCAS</sub> | OE low (reset) to nCASC delay                                  | _   | _   | 30  | ns    |

#### Note to Table 9:

Table 10 lists the timing parameters when using EPC1, EPC2, and EPC1441 devices at  $5.0~\rm{V}$ .

Table 10. Timing Parameters when Using EPC1, EPC2, and EPC1441 Devices at 5.0 V (Part 1 of 2)

| Symbol            | Parameter                                                      | Min | Тур | Max  | Units |

|-------------------|----------------------------------------------------------------|-----|-----|------|-------|

| t <sub>POR</sub>  | POR delay <sup>(1)</sup>                                       | _   | _   | 200  | ms    |

| t <sub>OEZX</sub> | OE high to DATA output enabled                                 | _   |     | 50   | ns    |

| t <sub>CE</sub>   | OE high to first rising edge on DCLK                           | _   | _   | 200  | ns    |

| t <sub>DSU</sub>  | Data setup time before rising edge on DCLK                     | 30  | _   | _    | ns    |

| t <sub>DH</sub>   | Data hold time after rising edge on DCLK                       | 0   | _   | _    | ns    |

| t <sub>CO</sub>   | DCLK to DATA out                                               | _   |     | 20   | ns    |

| t <sub>CDOE</sub> | DCLK to DATA enable/disable                                    | _   | _   | 20   | ns    |

| f <sub>CLK</sub>  | DCLK frequency                                                 | 6.7 | 10  | 16.7 | MHz   |

| t <sub>MCH</sub>  | DCLK high time for the first device in the configuration chain | 30  | 50  | 75   | ns    |

| t <sub>MCL</sub>  | DCLK low time for the first device in the configuration chain  | 30  | 50  | 75   | ns    |

| t <sub>SCH</sub>  | DCLK high time for subsequent devices                          | 30  | _   | _    | ns    |

| t <sub>SCL</sub>  | DCLK low time for subsequent devices                           | 30  | _   | _    | ns    |

| t <sub>CASC</sub> | DCLK rising edge to nCASC                                      |     | _   | 20   | ns    |

| t <sub>CCA</sub>  | nCS to nCASC cascade delay                                     |     | _   | 10   | ns    |

<sup>(1)</sup> During initial power-up, a POR delay occurs to permit voltage levels to stabilize. Subsequent reconfigurations do not incur this delay.

Page 18 Timing Information

Table 10. Timing Parameters when Using EPC1, EPC2, and EPC1441 Devices at 5.0 V (Part 2 of 2)

| Symbol             | Parameter                                             |     | Тур | Max | Units |

|--------------------|-------------------------------------------------------|-----|-----|-----|-------|

| t <sub>OEW</sub>   | OE low pulse width (reset) to guarantee counter reset | 100 | _   | _   | ns    |

| t <sub>OEC</sub>   | OE low (reset) to DCLK disable delay                  | _   | _   | 20  | ns    |

| t <sub>NRCAS</sub> | OE low (reset) to nCASC delay                         | _   | _   | 25  | ns    |

#### Note to Table 10:

(1) During initial power-up, a POR delay occurs to permit voltage levels to stabilize. Subsequent reconfigurations do not incur this delay.

Table 11 lists the timing parameters when using EPC1, EPC1064, EPC1064V, EPC1213, and EPC1441 devices when configuring the FLEX 8000 device.

Table 11. FLEX 8000 Device Configuration Parameters Using EPC1, EPC1064, EPC1064V, EPC1213, and EPC1441 Devices

| Symbol             | Parameter                                    | EPC1     | 064V |     | 64 and<br>1213 | d EPC1 and EPC1441 |     | Unit |

|--------------------|----------------------------------------------|----------|------|-----|----------------|--------------------|-----|------|

| •                  |                                              | Min      | Max  | Min | Max            | Min                | Max | Ī    |

| t <sub>OEZX</sub>  | OE high to DATA output enabled               | _        | 75   | _   | 50             | _                  | 50  | ns   |

| t <sub>CSZX</sub>  | ncs low to data output enabled               |          | 75   | _   | 50             | _                  | 50  | ns   |

| t <sub>CSXZ</sub>  | ncs high to data output disabled             | _        | 75   | _   | 50             | _                  | 50  | ns   |

| tcss               | ncs low setup time to first DCLK rising edge | 150      | _    | 100 | _              | 50                 | _   | ns   |

| t <sub>CSH</sub>   | ncs low hold time after DCLK rising edge     | 0        | _    | 0   | _              | 0                  | _   | ns   |

| t <sub>DSU</sub>   | Data setup time before rising edge on DCLK   | 75       | _    | 50  | _              | 50                 | _   | ns   |

| t <sub>DH</sub>    | Data hold time after rising edge on DCLK     | 0        | _    | 0   | _              | 0                  | _   | ns   |

| tco                | DCLK to DATA out delay                       | _        | 100  | _   | 75             | _                  | 75  | ns   |

| t <sub>CK</sub>    | Clock period                                 | 240      | _    | 160 | _              | 100                | _   | ns   |

| f <sub>CK</sub>    | Clock frequency                              | <u> </u> | 4    | _   | 6              | _                  | 8   | MHz  |

| t <sub>CL</sub>    | DCLK low time                                | 120      | _    | 80  | _              | 50                 | _   | ns   |

| t <sub>CH</sub>    | DCLK high time                               | 120      | _    | 80  | _              | 50                 | _   | ns   |

| t <sub>XZ</sub>    | OE low or ncs high to DATA output disabled   | <u> </u> | 75   | _   | 50             | _                  | 50  | ns   |

| t <sub>OEW</sub>   | OE pulse width to guarantee counter reset    | 150      | _    | 100 | _              | 100                | _   | ns   |

| t <sub>CASC</sub>  | Last DCLK + 1 to nCASC low delay             | -        | 90   | _   | 60             | _                  | 50  | ns   |

| t <sub>CKXZ</sub>  | Last DCLK + 1 to DATA tri-state delay        | -        | 75   | _   | 50             | _                  | 50  | ns   |

| t <sub>CEOUT</sub> | nCS high to nCASC high delay                 |          | 150  |     | 100            | _                  | 100 | ns   |

Operating Conditions Page 19

# **Operating Conditions**

Table 12 through Table 19 list information about absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for configuration devices.

Table 12. Absolute Maximum Ratings (1)

| Symbol           | Parameter                         | Conditions              | Min  | Max | Unit |

|------------------|-----------------------------------|-------------------------|------|-----|------|

| V <sub>CC</sub>  | Supply voltage                    | With respect to GND (2) | -2.0 | 7.0 | V    |

| VI               | DC input voltage                  | With respect to GND (2) | -2.0 | 7.0 | V    |

| I <sub>MAX</sub> | DC V <sub>CC</sub> or GND current | _                       | _    | 50  | mA   |

| I <sub>OUT</sub> | DC output current, per pin        | _                       | -25  | 25  | mA   |

| PD               | Power dissipation                 | _                       | _    | 250 | mW   |

| T <sub>STG</sub> | Storage temperature               | No bias                 | -65  | 150 | ° C  |

| T <sub>AMB</sub> | Ambient temperature               | Under bias              | -65  | 135 | ° C  |

| TJ               | Junction temperature              | Under bias              | _    | 135 | ° C  |

**Table 13. Recommended Operating Conditions**

| Symbol          | Parameter                          | Conditions          | Min            | Max                   | Unit |

|-----------------|------------------------------------|---------------------|----------------|-----------------------|------|

| V <sub>CC</sub> | Supply voltage for 5.0-V operation | (3), (4)            | 4.75<br>(4.50) | 5.25<br>(5.50)        | V    |

|                 | Supply voltage for 3.3-V operation | (3), (4)            | 3.0 (3.0)      | 3.6 (3.6)             | V    |

| VI              | Input voltage                      | With respect to GND | -0.3           | V <sub>CC</sub> + 0.3 | V    |

| V <sub>0</sub>  | Output voltage                     | _                   | 0              | V <sub>CC</sub>       | V    |

| m               | Operating temperature              | For commercial use  | 0              | 70                    | ° C  |

| T <sub>A</sub>  | Operating temperature              | For industrial use  | -40            | 85                    | ° C  |

| t <sub>R</sub>  | Input rise time                    | _                   | _              | 20                    | ns   |

| t <sub>F</sub>  | Input fall time                    | _                   | _              | 20                    | ns   |

**Table 14. DC Operating Conditions**

| Symbol          | Parameter                                 | Conditions                                  | Min                   | Max                   | Unit |

|-----------------|-------------------------------------------|---------------------------------------------|-----------------------|-----------------------|------|

| $V_{IH}$        | High-level input voltage                  | _                                           | 2.0                   | V <sub>CC</sub> + 0.3 | V    |

| $V_{IL}$        | Low-level input voltage                   | _                                           | -0.3                  | 0.8                   | V    |

| 7.7             | 5.0-V mode high-level TTL output voltage  | I <sub>OH</sub> = -4 mA DC <sup>(6)</sup>   | 2.4                   | _                     | V    |

| V <sub>OH</sub> | 3.3-V mode high-level CMOS output voltage | I <sub>OH</sub> = -0.1 mA DC <sup>(6)</sup> | V <sub>CC</sub> - 0.2 | _                     | V    |

| V <sub>OL</sub> | Low-level output voltage                  | I <sub>OL</sub> = 4 mA DC <sup>(6)</sup>    | _                     | 0.4                   | V    |

| II              | Input leakage current                     | $V_I = V_{CC}$ or GND                       | -10                   | 10                    | μА   |

| I <sub>OZ</sub> | Tri-state output off-state current        | $V_0 = V_{CC}$ or GND                       | -10                   | 10                    | μА   |

Page 20 Operating Conditions

#### Table 15. EPC1064, EPC1064V, and EPC1213 Devices I<sub>CC</sub> Supply Current Values

| Symbol           | Parameter                                             | Conditions | Min | Тур | Max | Unit |

|------------------|-------------------------------------------------------|------------|-----|-----|-----|------|

| I <sub>CCO</sub> | V <sub>CC</sub> supply current (standby)              | _          | _   | 100 | 200 | μΑ   |

| I <sub>CC1</sub> | V <sub>CC</sub> supply current (during configuration) |            | _   | 10  | 50  | mA   |

#### **Table 16. EPC2 Device Values**

| Symbol            | Parameter                                             | Conditions                             | Min | Тур | Max | Unit |

|-------------------|-------------------------------------------------------|----------------------------------------|-----|-----|-----|------|

| I <sub>CCO</sub>  | V <sub>CC</sub> supply current (standby)              | V <sub>CC</sub> = 5.0 V or 3.3 V       | _   | 50  | 100 | μΑ   |

| I <sub>CC1</sub>  | V <sub>CC</sub> supply current (during configuration) | V <sub>CC</sub> = 5.0 V or 3.3 V       | _   | 18  | 50  | mA   |

| R <sub>CONF</sub> | Configuration pins                                    | Internal pull up (OE, nCS, nINIT_CONF) | _   | 1   | _   | kΩ   |

### Table 17. EPC1 Device I<sub>CC</sub> Supply Current Values

| Symbol                          | Parameter                                             | Conditions              | Min | Тур | Max  | Unit |

|---------------------------------|-------------------------------------------------------|-------------------------|-----|-----|------|------|

| I <sub>CCO</sub>                | V <sub>CC</sub> supply current (standby)              | _                       | _   | 50  | 100  | μΑ   |

| I <sub>CC1</sub> V <sub>C</sub> | V <sub>CC</sub> supply current (during configuration) | V <sub>CC</sub> = 5.0 V | _   | 30  | 50   | mA   |

|                                 | V <sub>CC</sub> supply current (during configuration) | V <sub>CC</sub> = 3.3 V | _   | 10  | 16.5 | mA   |

#### Table 18. EPC1441 Device Icc Supply Current Values

| Symbol           | Parameter                                             | Conditions              | Min | Тур | Max | Unit |

|------------------|-------------------------------------------------------|-------------------------|-----|-----|-----|------|

| I <sub>CCO</sub> | V <sub>CC</sub> supply current (standby)              | _                       | _   | 30  | 60  | μΑ   |

| I <sub>CC1</sub> | V <sub>CC</sub> supply current (during configuration) | V <sub>CC</sub> = 5.0 V | _   | 15  | 30  | mA   |

| I <sub>CC1</sub> | V <sub>CC</sub> supply current (during configuration) | V <sub>CC</sub> = 3.3 V | _   | 5   | 10  | mA   |

#### Table 19. Capacitance (7)

| Symbol           | Parameter              | Conditions                          | Min | Max | Unit |

|------------------|------------------------|-------------------------------------|-----|-----|------|

| CIN              | Input pin capacitance  | V <sub>IN</sub> = 0 V, f = 1.0 MHz  | _   | 10  | pF   |

| C <sub>OUT</sub> | Output pin capacitance | V <sub>OUT</sub> = 0 V, f = 1.0 MHz | _   | 10  | pF   |

#### Notes to Table 12 through Table 19:

- (1) For more information, refer to the *Operating Requirements for Altera Devices Datasheet*.

- (2) The minimum DC input is -0.3 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 7.0 V for input currents less than 100 mA and periods shorter than 20 ns under no-load conditions.

- (3) Numbers in parentheses are for industrial temperature range devices.

- (4) Maximum  $V_{CC}$  rise time is 100 ms.

- (5) Certain EPC2 device pins are driven to 5.75~V when operated with a  $3.3-V~V_{CC}$ . For more information, refer to Table 4 on page 11.

- (6) The I<sub>OH</sub> parameter refers to high-level TTL or CMOS output current and the I<sub>OL</sub> parameter refers to low-level TTL or CMOS output current.

- (7) Capacitance is sample tested only.

Pin Information Page 21

### **Pin Information**

Table 20 lists the pin functions of the EPC1, EPC2, and EPC1441 devices during device configuration.

For more information about pin information of EPC devices, refer to the *Enhanced Configuration (EPC) Devices Datasheet*.

For more information about pin information of EPCS devices, refer to the *Serial Configuration (EPCS) Devices Datasheet*.

Table 20. EPC1, EPC2, and EPC1441 Device Pin Functions During Configuration (Part 1 of 3)

| Pin Name | Pin Number                   |                |                               |                             |                                                                                                                                                                                                                                                                                                      |

|----------|------------------------------|----------------|-------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 8-Pin<br>PDIP <sup>(1)</sup> | 20-Pin<br>PLCC | 32-Pin<br>TQFP <sup>(2)</sup> | Pin Type                    | Description                                                                                                                                                                                                                                                                                          |

| DATA     | 1                            | 2              | 31                            | Output                      | Serial data output. The DATA pin connects to the DATAO pin of the FPGA. DATA is latched into the FPGA on the rising edge of DCLK.                                                                                                                                                                    |

|          |                              |                |                               |                             | The DATA pin is tri-stated before configuration and when the nCS pin is high. After configuration, the EPC2 device drives DATA high, while the EPC1 and EPC1441 device tri-state DATA.                                                                                                               |

| DCLK     | 2                            | 4              | 2                             | Bidirectional               | Clock output when configuring with a single configuration device or when the configuration device is the first (master) device in a chain. Clock input for the next (slave) configuration devices in a chain. The DCLK pin connects to the DCLK pin of the FPGA.                                     |

|          |                              |                |                               |                             | Rising edges on DCLK increment the internal address counter and present the next bit of data on the DATA pin. The counter is incremented only if the OE input is held high, the ncs input is held low, and all configuration data has not been transferred to the target device.                     |

|          |                              |                |                               |                             | After configuration or when OE is low, the EPC1, EPC2 and EPC1441 device drive DCLK low.                                                                                                                                                                                                             |

| OE       | 3                            | 8              | 7                             | Open-drain<br>bidirectional | Output enable (active high) and reset (active low). The OE pin connects to the <code>nstatus</code> pin of the FPGA.                                                                                                                                                                                 |

|          |                              |                |                               |                             | A low logic level resets the address counter. A high logic level enables DATA and the address counter to count. If this pin is low (reset) during configuration, the internal oscillator becomes inactive and DCLK drives low. For more information, refer to "Error Detection Circuitry" on page 9. |

|          |                              |                |                               |                             | The OE pin has an internal programmable 1-kΩ resistor in EPC2 devices. If internal pull-up resistors are used, do not use external pull-up resistors on these pins. You can disable the internal pull-up resistors through the <b>Disable nCs and OE pull-ups on configuration device</b> option.    |

Page 22 Pin Information

Table 20. EPC1, EPC2, and EPC1441 Device Pin Functions During Configuration (Part 2 of 3)

| Pin Name      | Pin Number        |                |                               |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|---------------|-------------------|----------------|-------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|